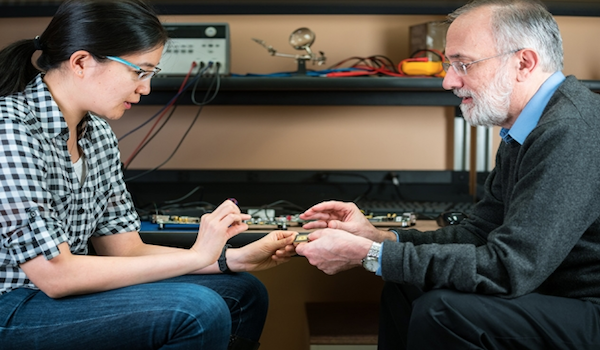

Vivienne Sze y Joel Emer enseñan Hardware Architecture for Deep Learning, una clase en el Departamento de Ingeniería Eléctrica e Informática del MIT que se enfoca en la construcción de hardware especializado para IA.La clase impartida por Vivienne Sze y Joel Emer reúne disciplinas tradicionalmente separadas para los avances en el aprendizaje profundo.

En una reciente mañana de lunes, Vivienne Sze, profesora asociada de ingeniería eléctrica e informática del MIT, habló con entusiasmo sobre el diseño de la arquitectura de red. Sus estudiantes asintieron lentamente, como si estuvieran a punto de comprender. Cuando el material hizo clic, los movimientos aumentaron en velocidad y confianza. “¿Todo está claro como el cristal?”, Preguntó con una breve pausa y un gesto de asentimiento antes de volver a sumergirse.

Este nuevo curso, 6.S082 / 6.888 ( Hardware Architecture for Deep Learning ), tiene un tamaño modesto, con un tope de 25 por ahora, en comparación con las salas de conferencias de estallido, características de otras clases de MIT centradas en el aprendizaje automático y la inteligencia artificial. Pero este curso es un poco diferente. Con una larga lista de requisitos previos y una gran base de conocimientos asumidos, los estudiantes están saltando a aguas profundas rápidamente. Resaltan el diseño algorítmico en unas pocas semanas, cubren el terreno del diseño de hardware de computadora en un período similar y luego se ponen manos a la obra: cómo pensar acerca de cómo hacer que estos dos campos funcionen juntos.

El objetivo de la clase es enseñar a los estudiantes la interacción entre dos disciplinas tradicionalmente separadas, dice Sze. “¿Cómo se pueden escribir algoritmos que se mapeen bien en el hardware para que puedan funcionar más rápido? ¿Y cómo puedes diseñar hardware para soportar mejor el algoritmo? “, Pregunta retóricamente. “Una cosa es diseñar algoritmos, pero para implementarlos en el mundo real debes tener en cuenta la velocidad y el consumo de energía”.

“Estamos comenzando a ver un gran interés de los estudiantes en el lado del hardware del aprendizaje profundo”, dice Joel Emer, quien ensena el curso con Sze. Un profesor de la práctica en el Departamento de Ingeniería Eléctrica e Informática del MIT, y un distinguido científico investigador del fabricante de chips NVidia, Emer se ha asociado anteriormente con Sze. Juntos, escribieron un artículo en una revista que ofrece un tutorial completo y una cobertura de encuestas de los avances recientes para permitir el procesamiento eficiente de redes neuronales profundas. Se usa como referencia principal para el curso.

En 2016, su grupo dio a conocer un nuevo chip de computadora con consumo eficiente de energía optimizado para redes neuronales, que podría permitir que poderosos sistemas de inteligencia artificial se ejecuten localmente en dispositivos móviles. El chip innovador, llamado “Eyeriss”, también podría ayudar a marcar el comienzo de Internet.

“He estado en este campo por más de cuatro décadas. Nunca he visto un área con tanta emoción y promesas en todo ese tiempo “, dice Emer. “La oportunidad de tener un impacto original a través de la construcción de una arquitectura importante y especializada es mayor que cualquier otra cosa que haya visto antes”.

Hardware en el corazón del aprendizaje profundo

El aprendizaje profundo es un nuevo nombre para una aproximación a la inteligencia artificial llamada redes neuronales, un medio para hacer aprendizaje automático en el cual una computadora aprende a realizar algunas tareas mediante el análisis de ejemplos de entrenamiento. Hoy, las aplicaciones populares de aprendizaje profundo están en todas partes, dice Emer. La técnica impulsa el reconocimiento de imágenes, los autos sin conductor, el análisis de imágenes médicas, los sistemas de vigilancia y transporte, y la traducción de idiomas, por ejemplo.

El valor del hardware en el corazón del aprendizaje profundo a menudo se pasa por alto, dice Emer. Las redes neuronales prácticas y eficientes, que los científicos informáticos han investigado de forma intermitente durante 60 años, eran inviables sin hardware para admitir algoritmos de aprendizaje profundo. “Muchos logros de AI fueron posibles gracias a los avances en hardware”, dice. “El hardware es la base de todo lo que puede hacer en software”.

Las técnicas de aprendizaje profundo están evolucionando muy rápidamente, dice Emer. “Hay una necesidad directa de este tipo de hardware. Algunos de los estudiantes que salen de la clase podrían contribuir a la revolución del hardware “.

Mientras tanto, compañías de software tradicionales como Google y Microsoft están tomando nota e invierten en hardware más personalizado para acelerar el procesamiento para el aprendizaje profundo, según Sze.

“Las personas están reconociendo la importancia de tener un hardware eficiente para apoyar el aprendizaje profundo”, dice ella. “Y hardware especializado para impulsar la investigación. Una de las mayores limitaciones del progreso en el aprendizaje profundo es la cantidad de cálculos disponibles “.

Nuevas arquitecturas de hardware

La implementación en el mundo real es clave para Skanda Koppula, un estudiante graduado en ingeniería eléctrica y ciencias de la computación. Es miembro del equipo de electrónica de carreras de autos MIT Formula SAE.

“Planeamos aplicar algunas de estas ideas en la construcción de sistemas de percepción para un automóvil de carrera de estudiantes sin fórmula de conductor”, dice. “Y en el largo plazo, me veo trabajando para obtener un doctorado en campos relacionados”.

Valerie Sarge, también estudiante de posgrado en ingeniería eléctrica e informática, está tomando el curso de preparación para una carrera que implica la creación de hardware para aplicaciones de aprendizaje automático.

“El aprendizaje profundo es un campo en rápido crecimiento, y las mejores arquitecturas de hardware tienen el potencial de tener un gran impacto en la capacidad de los investigadores para entrenar redes de manera efectiva”, dice ella. “A través de esta clase, estoy obteniendo algunas de las habilidades que necesito para contribuir al diseño de estas arquitecturas”.

Fuente: MIT